# IEEE Region 3 SoutheastCon 2021

## 3.3 kV 4H-SiC Planar-Gate MOSFETs Manufactured using Gen-5 PRESiCE<sup>™</sup> Technology in a 4-inch Wafer Commercial Foundry

#### Aditi Agarwal, B. Jayant Baliga

Dept. of Electrical and Computer Engineering NC State University, Raleigh, NC, USA

SoutheastCon 2021

Engineers Connecting the World

Email: aagarw12@ncsu.edu

Michel M.A. Francois, Ed Maxwell, Nathaniel Berliner, Marc Papageorge SiCamore Semi, Bend, OR, USA

Email: MFrancois@sicamoresemi.com

Date: 12 March, 2021

Advancing Technology for Humanity

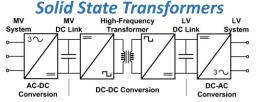

## **Applications for 3.3 kV Power Devices**

#### **Renewable Energy**

- Solar String Inverters

- Grid-tied Renewable Energy Conversion

- Energy Storage and Distribution

R. Takayanagi, et al, "3.3 kV All-SiC Module for Electric Distribution Equipment," In *IPEC-Niigata 2018-ECCE Asia*, pp. 3396-3400.

SoutheastCon 2021

Engineers Connecting the World

#### **Transportation**

- Railway Traction Systems

- EV Fast Chargers

K. Hamada et al, "3.3 kV/1500 A power modules for the world's first all-SiC traction inverter," *JJAP*, *54*(4S), 04DP07, 2015.

L. Gill, et al, "Medium Voltage Dual Active Bridge Using 3.3kV SiC MOSFETs for EV Charging Application," 2019 ECCE, USA, pp. 1237-1244.

### Medium Voltage Industrial Applications

Large industrial converters (cement, mining and minerals, metals, oil and gas etc.)

J. Hayes, et al, "Dynamic characterization of next generation medium voltage (3.3 kV, 10 kV) silicon carbide power modules," In *PCIM Europe 2017*, pp. 1-7.

H. Wen, et al, "Characterization and evaluation of 3.3 kv 5 a sic mosfet for solid-state transformer applications," In 2018 IEEE ACEPT, pp. 1-5.

#### 2

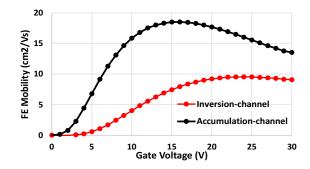

## **Gen-5 PRESiCE<sup>™</sup> Process**

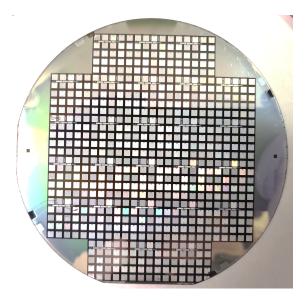

Fabricated wafer:

- C-V test structure measurements confirmed gate oxide thickness of 50 nm.

- Field-Effect Mobility was measured using long-channel FATFET test structure.

@ Gate voltage of 20 V:

- Accumulation-channel mobility is ~ 17 cm<sup>2</sup>/Vs.

- Inversion-channel mobility is ~ 9 cm<sup>2</sup>/Vs.

- Accumulation-channel mobility is higher due to reduced charge trapping at the n-Base/SiO<sub>2</sub> interface.

## **Wafer-level Measurements**

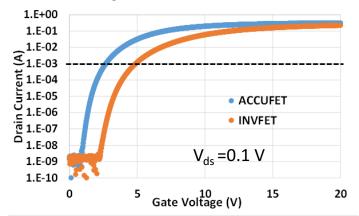

### **Transfer Characteristics**

V<sub>th</sub> for ACCUFET is lower than that for INVFET because of smaller band bending required to create a channel in case of an n-type base region.

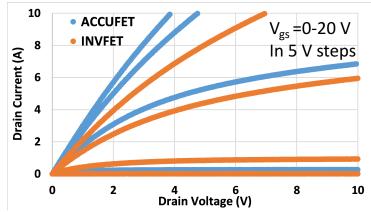

### **Output Characteristics**

ACCUFETs have better output characteristics and R<sub>on,sp</sub> compared to INVFET due to higher channel mobility and lower V<sub>th</sub>.

|                              |                                                               | ACCUFET                            | INVFET                             | $R_{CH,sp} \downarrow = \frac{L_{CH} W_{cell}}{2\mu_{CH} \uparrow C_{ox} (V_{gs} - V_{th} \downarrow)}$ |

|------------------------------|---------------------------------------------------------------|------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------|

|                              | V <sub>th</sub> @ I <sub>d</sub> =1mA                         | 2.7 V                              | 4.9 V                              |                                                                                                         |

|                              | R <sub>on,sp</sub> @ V <sub>gs</sub> =20V, I <sub>d</sub> =1A | $13.8 \text{ m}\Omega\text{-cm}^2$ | $19.8 \text{ m}\Omega\text{-cm}^2$ |                                                                                                         |

| Southeast<br>Engineers Conne |                                                               | 4                                  |                                    | <b>IEEE</b>                                                                                             |

# **Wafer-level Measurements**

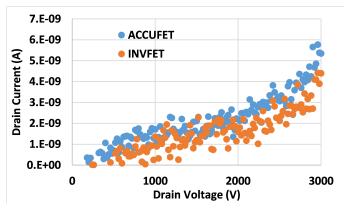

### **Blocking Characteristics**

- Both MOSFETs have very low leakage current < 10 nA up to 3 kV.

- Low leakage for ACCUFET implies that channel potential is sufficient to prevent reach-through breakdown.

### Southeast Con Atlanta 2021

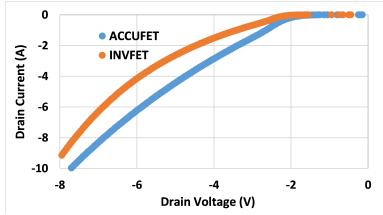

### **3**<sup>rd</sup> **Quadrant** Characteristics

INVFET has higher voltage drop in the 3<sup>rd</sup> quadrant at a fixed value of current due to its higher channel potential.

|                                                                                         | ACCUFET | INVFET |

|-----------------------------------------------------------------------------------------|---------|--------|

| 3 <sup>rd</sup> Quad V <sub>f</sub><br>@ I <sub>d</sub> =2.25 A (50 A/cm <sup>2</sup> ) | 3.6 V   | 4.7 V  |

## **Wafer-level Measurements**

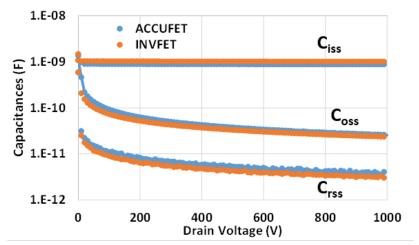

### Input, Output and Reverse Transfer Capacitances

Measured C<sub>iss</sub>, C<sub>oss</sub> and C<sub>rss</sub> are very close for both devices due to same basic cell structure.

Channel type does not affect capacitances.

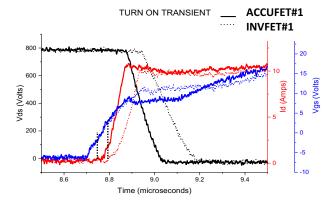

However, it has been shown previously that ACCUFETs have better switching performance compared to INVFETs with same device geometry, due to lower V<sub>th</sub> and higher transconductance.

A. Agarwal, et al, "Experimental Study of Switching and Short-Circuit Performance of 1.2 kV 4H-SiC Accumulation and Inversion Channel Power MOSFETs," ICSCRM 2019.

## **Summary and Conclusions**

| Region                                                | ACCUFET                            | INVFET                             |  |

|-------------------------------------------------------|------------------------------------|------------------------------------|--|

| $R_{on,sp} @ V_{gs}=20V, I_d=1A$                      | $13.8 \text{ m}\Omega\text{-cm}^2$ | $19.8 \text{ m}\Omega\text{-cm}^2$ |  |

| V <sub>th</sub> @ I <sub>d</sub> =1mA                 | 2.7 V                              | 4.9 V                              |  |

| $3^{rd}$ Quad V <sub>f</sub> @ I <sub>d</sub> =2.25 A | 3.6 V                              | 4.7 V                              |  |

| C <sub>iss,sp</sub> @ V <sub>ds</sub> =1 kV           | 19.4 nF/cm <sup>2</sup>            | 22.2 nF/cm <sup>2</sup>            |  |

| C <sub>oss,sp</sub> @ V <sub>ds</sub> =1 kV           | 0.6 nF/cm <sup>2</sup>             | 0.5 nF/cm <sup>2</sup>             |  |

| C <sub>rss,sp</sub> @ V <sub>ds</sub> =1 kV           | 80 pF/cm <sup>2</sup>              | 67 pF/cm <sup>2</sup>              |  |

| HF-FOM (R <sub>on</sub> *C <sub>rss</sub> )           | 1104 mΩ-pF                         | 1327 mΩ-pF                         |  |

- ➤ NCSU Gen-5 PRESiCE<sup>TM</sup> technology was used to establish a SiC power MOSFET manufacturing capability at a 4-inch wafer foundry operated by SiCamore Semi.

- 3.3 kV rated ACCUFETs and INVFETs were fabricated at SiCamore Semi with device performance consistent with state-of-the-art technology.

- Gate-Source Shorts were the yield limiting factor. Most devices had good leakage characteristics indicating robust edge termination.

- > Accumulation-channel structure enabled:

- 1.4 times lower specific on-resistance compared to the INVFET structure.

- Similar device capacitances as the INVFET structure

- 1.2 times lower HF-FOM (R<sub>on</sub>\*C<sub>rss</sub>) compared to the INVFET structure.

- SiCamore Semi can now be used by fabless companies for manufacturing SiC power devices.

#### SoutheastCon 2021 Engineers Connecting the World